Phase란 무엇인가요?

Phase(단계)는 시뮬레이션의 진행을 체계적으로 관리하기 위해 사용됩니다. UVM Phase는 테스트벤치의 동작을 구조화하고, 특정 작업을 순차적으로 수행하도록 돕는 역할을 합니다. 이는 복잡한 테스트 환경에서 동기화 문제를 줄이고, 코드의 재사용성과 가독성을 높이기 위해 설계되었습니다. -GPT-

UVM의 모든 component(driver, agent 등)들은 uvm_component라는 Class에서 파생됩니다. 또한 시뮬레이션할 때, 모든 component들이 동기화되어 각 단계에 따라 순차적으로 작동합니다. 우리는 이것을 synchronizing mechanism을 따른다고 합니다. 그리고 이러한 동기화를 가능하게 해주는 것이 phase 라는 컨셉입니다.

Phase가 왜 필요한가요?

일반적인 Verilog는 Static한 module이나 container로 이루어져 있습니다. 모든 모듈은 시뮬레이션을 시작할 때 생성되며, 도중에 모듈이 생성되거나 component가 호출되지 않습니다(구조가 변하지 않습니다). 즉, Verilog 테스트벤치는 기능이 제한적이며 확장성이 없습니다. 하지만 SystemVerilog는 OOP(객체 지향 프로그래밍) 기능의 도입으로 게임 전체를 변화시킵니다.

- SystemVerilog에서는 Class의 개념을 사용하여 필요할 때 재사용하고 확장할 수 있는 구조화된 독립체(여기서는 객체, uvm component를 말함. uvm component는 모두 class의 type을 가짐)를 만들 수 있습니다.

- 이러한 Class 객체들은 전체 시뮬레이션 중간에 생성되는 것이 가능합니다.

- 하지만 생성되는 타이밍, 호출되는 타이밍이 잘못되면 오류가 발생할 수 있습니다.

- 예를 들어, component가 아직 초기화되지 않은 상태에서 호출되면 잘못된 테스트벤치 출력이 발생할 수 있습니다. 또는 아직 호출되지 않은 component를 사용하여 하면 오류가 발생합니다.

- 따라서 제대로된 재사용성과 확장성을 위해서는, 테스트벤치 component 간의 동기화가 핵심 요구 사항입니다.

Phase에는 무엇이 있나요?

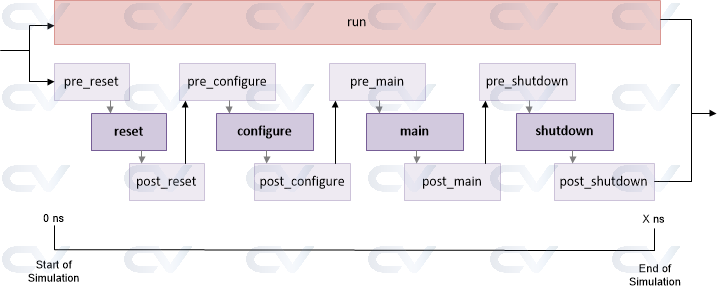

Phase를 크게 3단계로 구분합니다.

1. Build time phase

2. Run time phase

3. Clean-Up phase

더 자세하게 보면 다음 표와 같습니다.

Main UVM Phase

- Build와 Clean phase는 function type이며 hierarchy가 실행순서에 영향을 줍니다.

- build phase는 uvm_component들의 hierarchy 상위에서 하위로 실행을 합니다. 예를 들어, agent 내부에 driver와 monitor가 있다고 하면 agent의 build phase 먼저 실행됩니다. 상위 component가 있어야 하위 component가 생성될 수 있기 때문입니다.

- 이외의 다른 phase들은 하위에서 상위로 실행을 합니다.

- 코드를 작성할 때, 모든 phase를 작성해줄 필요는 없습니다. 필요한 경우에만 작성하면 됩니다. build와 connect, run phase는 거의 필수적으로 작성되긴 합니다. 다른 phase는 작성안해도 작동할 수 있습니다.

Build phase

Agent

class agent extends uvm_agent;

`uvm_component_utils(agent)

function new(string name="agent", uvm_component parent=null);

super.new(name, parent);

endfunction

driver d0; // Driver handle

monitor m0; // Monitor handle

uvm_sequencer #(Item) s0; // Sequencer Handle

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

s0 = uvm_sequencer#(Item)::type_id::create("s0", this);

d0 = driver::type_id::create("d0", this);

m0 = monitor::type_id::create("m0", this);

endfunction

...- Agent의 build_phase까지만 작성해보았습니다.

- Build Phase는 Agent의 하위 component들을 create하는 phase입니다.

Run Phase

- 유연성을 위해 pre, post가 붙은 phase도 있으며,

- task type으로 작성되어 유일하게 시간이 흐를 수 있는 phase입니다.

추후 알게되는 개념들이 있다면 더 자세하게 작성하여 추가하겠습니다.

더 자세한 내용은 제가 참고한 https://wikidocs.net/170348, https://www.chipverify.com/uvm/uvm-phases 사이트를 참고하셔도 좋을 것 같습니다!

읽어주셔서 감사합니다!

댓글, 지적, 하트와 댓글 부탁드립니다~><

https://velog.io/@onething818/posts

onething818 (장원) / 작성글 - velog

velog.io

제 벨로그에 더 많은 내용이 담겨있습니다! 많은 방문 부탁드립니다.

'UVM' 카테고리의 다른 글

| [UVM] Base가 되는 Classes (0) | 2024.12.26 |

|---|---|

| [UVM] UVM 검증방법론의 개념과 구조 (0) | 2024.12.26 |